Linux | Makefile

29 Oct 2021

인하대학교 컴퓨터공학과 이어진 교수님 리눅스프로그래밍 수업을 바탕으로 정리한 내용입니다.

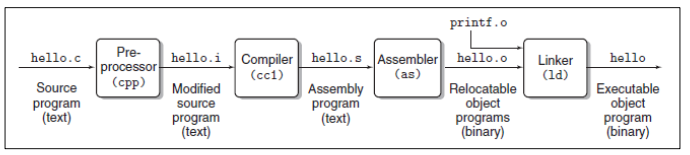

Compile 과정

- vim editor : source program 작성

- Pre-processor(cpp) : souce program을 modified source program으로 전환. ( #include, #define, 주석 제거)

- Compiler : modified source program을 assembly program으로 변환

- Linker(Id) : 여러 object file을 묶어 하나의 실행 file 생성

gcc hello.c -o hello.out: hello.out(실행 파일) 생성

Compile 옵션

-o: 출력 하고자 하는 실행 파일 설정-O: 최적화 옵션. -On(n=0, 1, 2, 3)에서 n에 따라 최적화 레벨 결정. 큰 숫자 일수록 더 최적화한다는 의미.-c: Linking을 수행하지 않고 object 파일까지만 생성. object 파일은 filename.o로 생성됨-S: Assembly 코드 생성. filename.s로 생성됨.-g: debugging을 위한 flag를 심어 컴파일- -Ipathname(헤더 파일 경로 설정), -Ilibrary(library 이름의 lib 추가), -Ldirectory (library 경로지정), -static(static linking, default는 dynamic linking)

Compile program with multi files using gcc

-

각 source file로 object 파일 생성

$gcc -c -o main.o main.c $gcc -c -o func.o func.c -

object 파일을 묶어(linking) 실행 파일 생성.

$gcc -o print_func main.o func.o -

생성된 실행파일 실행

$ ./print_func

Makefile

- Makefile

- 컴파일 시 필요한 규칙을 명시한 스크립트 파일

- 파일들이 어떻게 서로 의존하고 있는지, target을 어떻게 빌드해야 하는지 명세한 파일

- make 유틸리티가 Makefile을 처리함

-

Makefile 기본 작성법

all : <target> <target> : <dependency> <recipe> clean: <remove command>target: 빌드 이름 대상. rule이 만드는 최종 파일명dependency: 빌드 대상이 의존하는 파일 목록recipe: 빌드 대상을 생성하는 명령clean: make clean 명령어를 수행할 작업 작성. (build 부산물 정리)- 기본적으로 make을 이용하여 Makefile을 컴파일하면 all에 대해서 실행된다.

- receipe나 remove command 앞에서는 무조건 tab (space 안됨)으로 공백을 구분해야한다.

all : print_func print_func : main.o funco gcc -o print_func main.o func.o main.o : header.h main.c gcc -c main.c func.o : header.h func.c gcc -c func.c clean : rm -f *.o print_func

make : compile

- make 명령어를 통해 Makefile에 명시된 compile 수행 가능.

make target -f makefilename: target은 컴파일할 최종 목표, 생략시 all. makefilename은 Makefile 지정, 생략시 “Makefile”로 자동 지정.

jimmy@jimmy-VirtualBox:~/linux_programming$ make

gcc -g -O -c -o main.o main.c

gcc -g -O -c -o func.o func.c

gcc -g -O -o print_func main.o func.o

jimmy@jimmy-VirtualBox:~/linux_programming$ make clean

rm -f *.o print_func

Makefile 개선

- 매크로(변수) 사용

- 정의 : VAR = arguments

- 사용 : $(VAR)

- 가장 흔히 사용하는 매크로

- CC : 컴파일러

- CFLAGS : 컴파일 옵션

- OBJS : 중간 산물 Object 파일 목록

- TARGET : 빌드 대상(실행파일) 이름

make -p: make에서 사용하는 정의된 매크로 확인 가능

CC=gcc

CFLAGS= -g -O

OBJS=main.o func.o

TARGET=print_func

$(TARGET): $(OBJS)

$(CC) $(CFLAGS) -o $(TARGET) $(OBJS)

main.o: header.h main.c

func.o: header.h func.c

clean:

rm -f *.o print_func